<<برای مطالعه مقالات آموزشی رایگان مرتبط با FPGA به بخش مقالات مراجعه نمایید>>

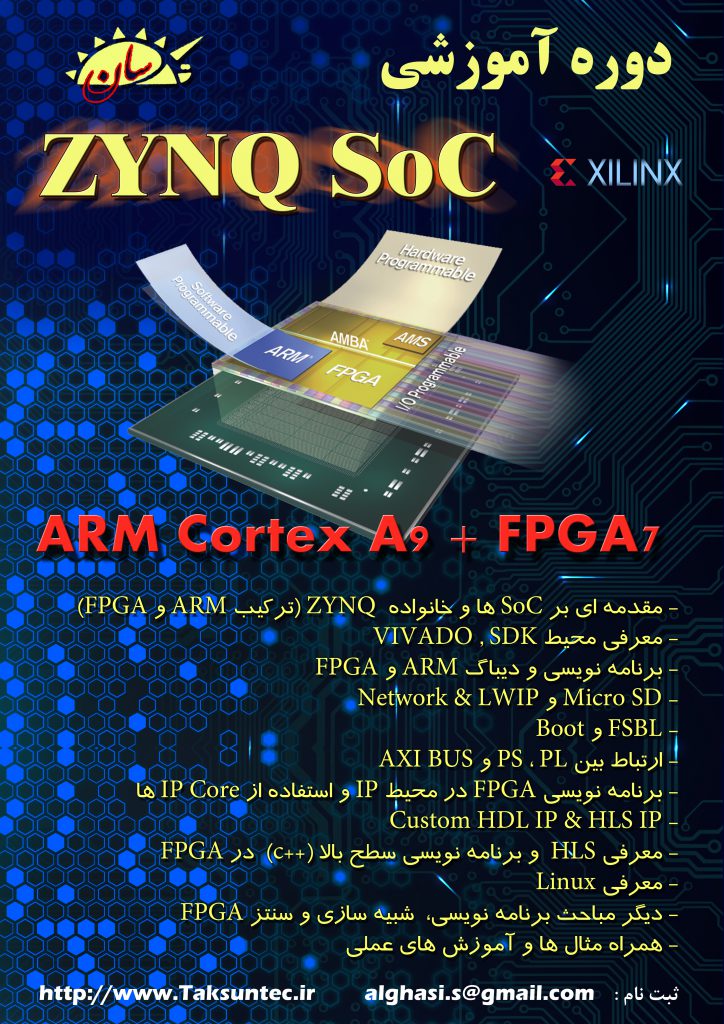

تکسان مفتخر است اولین برگزار کننده رسمی دورهای برنامه نویسی نوین FPGA در کشور است. این دوره ها شامل ZYNQ SoC ، HLS و … می باشد که از سال ۱۳۹۴ به صورت عمومی برگزار می گردد.

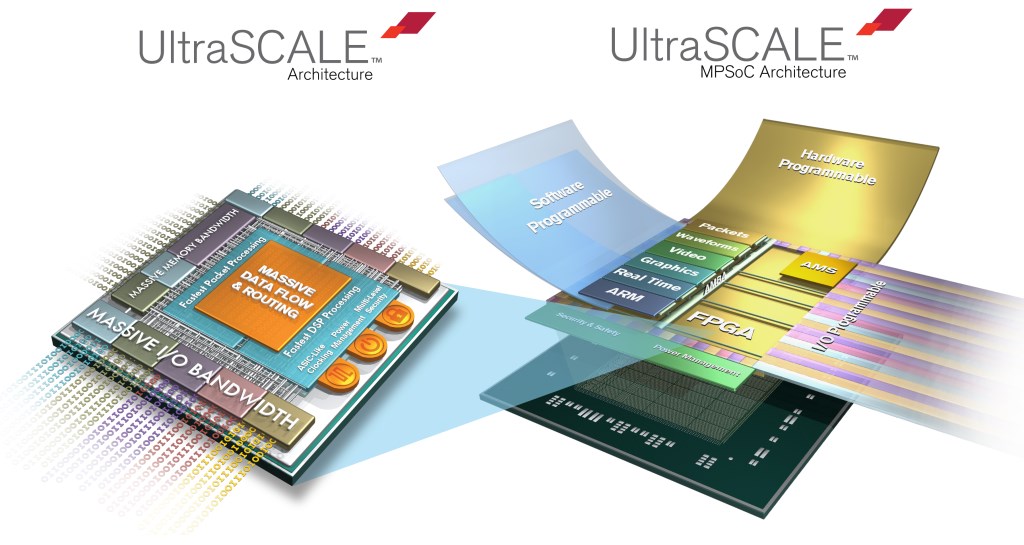

طراحی FPGA ها ی سری ۷ با رویکرد ZYNQ-7000

با توجه به اینکه ZYNQ شامل پردازنده و FPGA است، در طراحی سخت افزار بایستی هم به نکات پردازنده ها و هم به نکات FPGA ها توجه گردد. در این رویداد به طراحی شماتیک ZYNQ-7000 و بیان نکاتی که بایستی در طراحی PCB های این چیپ ها رعایت گردد اشاره می شود. هم چنین نکات مربوط به ادوات جانبی روی برد مانند شبکه، DDR و … ، و هم چنین تداخل های مختلف تنظیمات آنها بررسی می گردد.

به منظور افزایش حداکثری کاربردی بودن کلاس های آموزشی، همکاری با شرکت آرتمیش کاریا را آغاز نموده ایم. هنرجویان برتر بعد از گذراندن کلاس های آموزشی توسط این مرکز در صنعت های مختلف کشور جذب می شوند تا بتوانند در پیشرفت صنعت کشور سهیم باشند.

دوره ها هم به صورت حضوری هم به صورت برخط برگزار میگردد.

نکات:

- تمرکز این دوره بر استفاده از امکانات ZYNQ ، استفاده از IP Core ها و برنامه نویسی در Block Design است.

- مثال های عملی با برد های شرکت آرتمیس کاریا انجام می شود ولی مطالب و پروژه ها با تمامی برد های ZYNQ سازگار هستند.

پیش نیاز:

هزینه دوره : ۷،۸۰۰،۰۰۰ تومان

ثبت نام :

دوره آموزش عملی ZYNQ در VIVADO

سرفصل های آموزشی:

کار با وقفه ها و برنامه نویسی وقفه ها

- کار با وقفه های Shared Peripheral Interrupt (SPI)

- کار با وقفه های Software Generated Interrupt (SGI)

- معرفی وقفه های Private Peripheral Interrupt (PPI)

- ایجاد وقفه اختصاصی برای هر CPU

- انجام مثال های وقفه PL-PS

برنامه نویسی دو هسته ای

- بدون سیستم عامل

- مدیریت حافظه هر CPU

- ارتباط بین دو هسته و Mail Box

- بوت دوهسته ای

برنامه شبکه

- فعال سازی شبکه دوم به صورت Extended

- فعال سازی و ساخت AXI Ethernet شبکه دوم (یا چندین شبکه)

- استفاده از شبکه دوم در PL

- استفاده از LWIP با دو شبکه

- برنامه ftp و Web Server در LWIP

نکات پورت HP و DMA پیشرفته

- نکات کار با HP

- نکات استفاده از چند DMA

- DMA با Scatter Gader

- DMA با Interrupt

کار با XADC و آنالگ

- XADC PS

- XADC PL

- انجام پروژه با XADC With DMA & FFT

Security & Encryption

- بوت به صورت Secure

- رمز نگاری AES

- امضاء دیجیتال و رمز نگاری RSA

- ساخت کلید AES و RSA

- برنامه ریزی BBRAM و eFUSE

- توضیحاتی از bootgen و boot utility

انواع روش های برنامه ریزی و تغییر برنامه

- توضیحاتی از bootgen و boot utility

- تغییر در boot.bin

- برنامه ریزی از طریق شبکه

- کار با device config و PCAP

- تغییر برنامه bitstream در زمان دلخواه توسط PS

- Dual Boot

- Golden Boot

کار با پردازنده بخش DMA PS

- معرفی کنترلر مخصوص DMA

- کار با DMA PS

- انتقال داده با سرعت بالا

- برنامه نویسی کنترلر DMA

- انتقال داده بین حافظه و AXI ها

- وقفه DMA

- رابط های event/statuse / request بین PS و PL

- نکات BURST

کار با گذرگاه AXI ACP و شتاب دهنده سخت افزاری در PL

- معرفی AXI ACP

- نکات کلیدی cache و SCU

- انتقال داده با سرعت بالا

- ساخت شتابدهنده سخت افزاری با سرعت بالا در PL

- رابط مخصوص event و status برای CPU ها در PL

نکات جانبی و برنامه نویسی

- نکاتی در مورد Snoop Controller Unit (SCU)

- نکاتی درمورد Time & sys tick

- کار با Watch dog

- مشکلات کار با eMMC و eMMC Linux boot

- کار با FSBL Hooks

- Reset پردازنده و Reset PL